MICROCHIP PIC24 Flash-programmering

Produktinformation

Flash programmering

dsPIC33/PIC24-familierne af enheder har en intern programmerbar Flash-programhukommelse til udførelse af brugerkode. Der er op til tre metoder til at programmere denne hukommelse:

- Tabel Instruktion Betjening

- In-Circuit Serial Programmering (ICSP)

- In-Application Programming (IAP)

Tabelinstruktioner angiver metoden til overførsel af data mellem Flash-programhukommelsespladsen og datahukommelsespladsen på dsPIC33/PIC24-enheder. TBLRDL-instruktionen bruges til at læse fra bit[15:0] af programhukommelsesplads. TBLWTL-instruktionen bruges til at skrive til bit[15:0] af Flash-programhukommelsesplads. TBLRDL og TBLWTL kan få adgang til Flash-programhukommelse i Word-tilstand eller Byte-tilstand.

Ud over Flash-programhukommelsesadressen specificerer tabelinstruktionen også et W register (eller en W Register Pointer til en hukommelsesplacering), dvs. kilden til Flash-programhukommelsesdataene, der skal skrives, eller destinationen for et Flash-program hukommelse læst.

Dette afsnit beskriver teknikken til programmering af Flash-programhukommelse. dsPIC33/PIC24-familierne af enheder har en intern programmerbar Flash-programhukommelse til udførelse af brugerkode. Der er op til tre metoder til at programmere denne hukommelse:

- Run-Time Self-Programming (RTSP)

- In-Circuit Serial Programming™ (ICSP™)

- Enhanced In-Circuit Serial Programming (EICSP)

RTSP udføres af applikationssoftwaren under udførelsen, mens ICSP og EICSP udføres fra en ekstern programmør ved hjælp af en seriel dataforbindelse til enheden. ICSP og EICSP tillader meget hurtigere programmeringstid end RTSP. RTSP-teknikker er beskrevet i afsnit 4.0 "Run-Time Self-Programming (RTSP)". ICSP- og EICSP-protokollerne er defineret i programmeringsspecifikationsdokumenterne for de respektive enheder, som kan downloades fra mikrochippen webwebsted (http://www.microchip.com). Ved programmering i C-sproget er flere indbyggede funktioner tilgængelige, der letter Flash-programmering. Se "MPLAB® XC16 C Compiler User's Guide" (DS50002071) for detaljer om indbyggede funktioner.

Produktbrugsvejledning

Følg disse trin for at programmere Flash-programhukommelsen:

- Se enhedsdatabladet for at kontrollere, om afsnittet om familiereferencemanualen understøtter den enhed, du bruger.

- Download enhedsdatabladet og familiereferencemanualsektionerne fra Microchip Worldwide Webwebsted på: http://www.microchip.com.

- Vælg en af de tre metoder til at programmere hukommelsen (Tabel Instruction Operation, In-Circuit Serial Programming (ICSP), In-Application Programming (IAP)).

- Hvis du bruger Table Instruction Operation, skal du bruge TBLRDL-instruktionen til at læse fra bit[15:0] af programhukommelsesplads og TBLWTL-instruktionen til at skrive til bit[15:0] af Flash-programhukommelsesplads.

- Sørg for at angive et W-register (eller en W Register-peger til en hukommelsesplacering) som kilden til de Flash-programhukommelsesdata, der skal skrives, eller destinationen for en Flash-programhukommelseslæsning.

For yderligere information og detaljer om programmering af Flash-programhukommelsen henvises til dsPIC33/PIC24 Family Reference Manual.

TABEL INSTRUKTION BETJENING

Tabelinstruktionerne angiver metoden til overførsel af data mellem Flash-programhukommelsespladsen og datahukommelsespladsen på dsPIC33/PIC24-enheder. Dette afsnit giver en oversigt over de tabelinstruktioner, der bruges under programmering af Flash-programhukommelsen. Der er fire grundlæggende tabelinstruktioner:

- TBLRDL: Tabel læst lav

- TBLRDH: Tabel Læs Høj

- TBLWTL: Tabel Skriv lav

- TBLWTH: Tabel Skriv højt

TBLRDL-instruktionen bruges til at læse fra bit[15:0] af programhukommelsesplads. TBLWTL-instruktionen bruges til at skrive til bits[15:0] af Flash-programhukommelsesplads. TBLRDL og TBLWTL kan få adgang til Flash-programhukommelse i Word-tilstand eller Byte-tilstand.

TBLRDH- og TBLWTH-instruktionerne bruges til at læse eller skrive til bits[23:16] af programhukommelsesplads. TBLRDH og TBLWTH kan få adgang til Flash-programhukommelse i Word- eller Byte-tilstand. Fordi Flash-programhukommelsen kun er 24 bit bred, kan TBLRDH- og TBLWTH-instruktionerne adressere en øvre byte af Flash-programhukommelse, som ikke eksisterer. Denne byte kaldes "fantombyten". Enhver læsning af fantombyten vil returnere 0x00. En skrivning til fantombyten har ingen effekt. 24-bit Flash-programhukommelsen kan betragtes som to side om side 16-bit mellemrum, hvor hvert rum deler det samme adresseområde. Derfor får TBLRDL- og TBLWTL-instruktionerne adgang til den "lave" programhukommelsesplads (PM[15:0]). TBLRDH- og TBLWTH-instruktionerne får adgang til den "høje" programhukommelsesplads (PM[31:16]). Enhver læsning eller skrivning til PM[31:24] vil få adgang til phantom (uimplementeret) byte. Når nogen af tabelinstruktionerne bruges i bytetilstand, vil den mindst signifikante bit (LSb) af tabeladressen blive brugt som bytevalgsbit. LSb'en bestemmer, hvilken byte i det høje eller lave programhukommelsesrum, der tilgås.

Figur 2-1 illustrerer, hvordan Flash-programhukommelsen adresseres ved hjælp af tabelinstruktionerne. En 24-bit programhukommelsesadresse dannes ved hjælp af bits[7:0] af TBLPAG-registret og den effektive adresse (EA) fra et W-register specificeret i tabelinstruktionen. 24-bit programtælleren (PC) er illustreret i figur 2-1 til reference. De øverste 23 bits af EA'en bruges til at vælge Flash-programhukommelsesplaceringen.

Til byte-tilstandstabelinstruktionerne bruges LSb'et i W-registret EA til at vælge, hvilken byte af 16-bit Flash-programhukommelsesordet, der adresseres; '1' vælger bit[15:8] og '0' vælger bit[7:0]. LSb i W-registret EA ignoreres for en tabelinstruktion i Word-tilstand. Ud over Flash-programhukommelsesadressen specificerer tabelinstruktionen også et W register (eller en W Register Pointer til en hukommelsesplacering), dvs. kilden til Flash-programhukommelsesdataene, der skal skrives, eller destinationen for et Flash-program hukommelse læst. For en tabelskrivningsoperation i bytetilstand ignoreres bits[15:8] i kildearbejdsregisteret.

Brug af tabel Læs instruktioner

Tabellæsning kræver to trin:

- Adressemarkøren er sat op ved hjælp af TBLPAG-registret og et af W-registrene.

- Flash-programhukommelsens indhold på adresseplaceringen kan læses.

- LÆS ORD TILSTAND

Koden vist i Example 2-1 og ExampAfsnit 2-2 viser, hvordan man læser et ord i Flash-programhukommelsen ved hjælp af tabelinstruktionerne i Word-tilstand.

- LÆS BYTE-TILSTAND

Koden vist i ExampAfsnit 2-3 viser post-increment-operatoren på læsningen af den lave byte, hvilket får adressen i arbejdsregisteret til at stige med én. Dette sætter EA[0] til en '1' for adgang til den midterste byte i den tredje skriveinstruktion. Den sidste post-increment sætter W0 tilbage til en lige adresse, der peger på den næste Flash-programhukommelsesplacering.

- BORD SKRIVE LÅSE

Tabelskriveinstruktioner skriver ikke direkte til den ikke-flygtige programhukommelse. I stedet indlæser tabellen skriveinstruktioner skrivelåse, der lagrer skrivedataene. NVM-adresseregistrene skal indlæses med den første adresse, hvor låste data skal skrives. Når alle skrivelåsene er blevet indlæst, startes den egentlige hukommelsesprogrammeringsoperation ved at udføre en speciel sekvens af instruktioner. Under programmering overfører hardwaren dataene i skrivelåsene til Flash-hukommelsen. Skrivelåsene starter altid ved adressen 0xFA0000 og strækker sig gennem 0xFA0002 for ordprogrammering eller gennem 0xFA00FE for enheder, der har rækkeprogrammering.

Note: Antallet af skrivelåse varierer efter enhed. Se kapitlet "Flash Program Memory" i det specifikke enhedsdatablad for antallet af tilgængelige skrivelåse.

KONTROLREGISTER

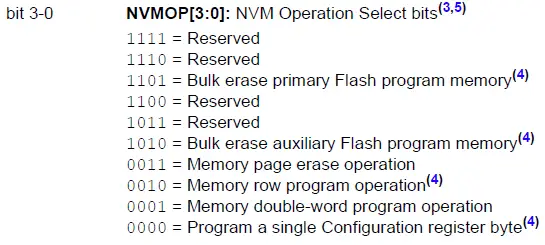

Adskillige specialfunktionsregistre (SFR'er) bruges til at programmere slette- og skriveoperationer i Flash-programhukommelsen: NVMCON, NVMKEY og NVM-adresseregistrene NVMADR og NVMADRU.

NVMCON Register

NVMCON-registret er det primære kontrolregister for Flash- og programmerings-/sletningsoperationer. Dette register vælger, om der skal udføres en sletning eller en programoperation, og kan starte program- eller slettecyklussen. NVMCON-registret er vist i register 3-1. Den nederste byte af NVMCON konfigurerer den type NVM-handling, der skal udføres.

NVMKEY Register

NVMKEY-registret (se register 3-4) er et skrivebeskyttet register, der bruges til at forhindre utilsigtede skrivninger af NVMCON, der kan ødelægge Flash-hukommelsen. Når den er låst op, tillades skrivning til NVMCON i én instruktionscyklus, hvor WR-bitten kan indstilles til at påkalde en slette- eller programmeringsrutine. I betragtning af tidskravene er det nødvendigt at deaktivere afbrydelser.

Udfør følgende trin for at starte en slette- eller programmeringssekvens:

- Deaktiver afbrydelser.

- Skriv 0x55 til NVMKEY.

- Skriv 0xAA til NVMKEY.

- Start programmeringsskrivecyklussen ved at indstille WR-bit (NVMCON[15]).

- Udfør to NOP-instruktioner.

- Gendan afbrydelser.

DEAKTIVERING AF AFBRYDELSER

Deaktivering af interrupts er påkrævet for alle Flash-handlinger for at sikre et vellykket resultat. Hvis der opstår en afbrydelse under NVMKEY-oplåsningssekvensen, kan den blokere skrivningen til WR-bitten. NVMKEY-oplåsningssekvensen skal udføres uden afbrydelse, som beskrevet i afsnit 3.2 "NVMKEY Register".

Interrupts kan deaktiveres på en af to metoder, ved at deaktivere Global Interrupt Enable (GIE-bit) eller ved at bruge DISI-instruktionen. DISI-instruktionen anbefales ikke, da den kun deaktiverer afbrydelser af prioritet 6 eller derunder; Derfor bør metoden Global Interrupt Enable bruges.

CPU-skrivning til GIE tager to instruktionscyklusser, før den påvirker kodestrømmen. To NOP-instruktioner er nødvendige bagefter, eller de kan erstattes med andre nyttige arbejdsinstruktioner, såsom indlæsning af NVMKEY; dette gælder både for faste og klare operationer. Der skal udvises forsigtighed ved genaktivering af afbrydelser, så den NVM-målrettede rutine ikke tillader afbrydelser, når en tidligere kaldt funktion har deaktiveret dem af andre årsager. For at løse dette i Assembly kan et stack push og pop bruges til at bevare tilstanden af GIE-bitten. I C kan en variabel i RAM bruges til at gemme INTCON2 før sletning af GIE. Brug følgende sekvens til at deaktivere afbrydelser:

- Skub INTCON2 på stakken.

- Ryd GIE-bitten.

- To NOP'er eller skriver til NVMKEY.

- Start programmeringscyklussen ved at indstille WR bit (NVMCON[15]).

- Gendan GIE-tilstand ved POP af INTCON2.

NVM-adresseregistre

De to NVM-adresseregistre, NVMADRU og NVMADR, danner, når de er sammenkædet, 24-bit EA for den valgte række eller det valgte ord til programmeringsoperationer. NVMADRU-registret bruges til at holde de øverste otte bit af EA, og NVMADR-registret bruges til at holde de nederste 16 bit af EA. Nogle enheder kan referere til de samme registre som NVMADRL og NVMADRH. NVM-adresseregistrene skal altid pege på en dobbelt instruktionsordgrænse, når der udføres en dobbeltinstruktionsordprogrammeringsoperation, en rækkegrænse ved udførelse af en rækkeprogrammeringsoperation eller en sidegrænse, når der udføres en sidesletningsoperation.

Register 3-1: NVMCON: Flash-hukommelseskontrolregister

Note

- Denne bit kan kun nulstilles (dvs. slettes) på en Power-on Reset (POR).

- Når du forlader inaktiv tilstand, er der en opstartsforsinkelse (TVREG), før Flash-programhukommelsen bliver operationel. Se kapitlet "Elektriske egenskaber" i det specifikke enhedsdatablad for mere information.

- Alle andre kombinationer af NVMOP[3:0] er uimplementerede.

- Denne funktionalitet er ikke tilgængelig på alle enheder. Se kapitlet "Flash-programhukommelse" i det specifikke enhedsdatablad for tilgængelige funktioner.

- Adgang til en strømbesparende tilstand efter udførelse af en PWRSAV-instruktion er betinget af fuldførelse af alle afventende NVM-operationer.

- Denne bit er kun tilgængelig på enheder, der understøtter RAM-bufferet rækkeprogrammering. Se det enhedsspecifikke datablad for tilgængelighed.

Note

- Denne bit kan kun nulstilles (dvs. slettes) på en Power-on Reset (POR).

- Når du forlader inaktiv tilstand, er der en opstartsforsinkelse (TVREG), før Flash-programhukommelsen bliver operationel. Se kapitlet "Elektriske egenskaber" i det specifikke enhedsdatablad for mere information.

- Alle andre kombinationer af NVMOP[3:0] er uimplementerede.

- Denne funktionalitet er ikke tilgængelig på alle enheder. Se kapitlet "Flash-programhukommelse" i det specifikke enhedsdatablad for tilgængelige funktioner.

- Adgang til en strømbesparende tilstand efter udførelse af en PWRSAV-instruktion er betinget af fuldførelse af alle afventende NVM-operationer.

- Denne bit er kun tilgængelig på enheder, der understøtter RAM-bufferet rækkeprogrammering. Se det enhedsspecifikke datablad for tilgængelighed.

Register 3-2: NVMADRU: Ikke-flygtig hukommelse Øvre adresseregister

Register 3-3: NVMADR: Ikke-flygtig hukommelsesadresseregister

Register 3-4: NVMKEY: Ikke-flygtig hukommelsesnøgleregister

SELVPROGRAMMERING TIL LØBETID (RTSP)

RTSP giver brugerapplikationen mulighed for at ændre indholdet i Flash-programhukommelsen. RTSP opnås ved hjælp af TBLRD (Tabel Read) og TBLWT (Table Write) instruktionerne, TBLPAG registret og NVM kontrol registrene. Med RTSP kan brugerapplikationen slette en enkelt side Flash-hukommelse og programmere enten to instruktionsord eller op til 128 instruktionsord på visse enheder.

RTSP-drift

The dsPIC33/PIC24 Flash program memory array is organized into erase pages that can contain up to 1024 instructions. The double-word programming option is available in all devices in the dsPIC33/PIC24 families. In addition, certain devices have row programming capability, which allows the programming of up to 128 instruction words at a time. Programming and erase operations always occur on an even double programming word, row or page boundaries. Refer to the “Flash Program Memory” chapter of the specific device data sheet for the availability and sizes of a programming row, and the page size for erasing. The Flash program memory implements holding buffers, called write latches, that can contain up to 128 instructions of programming data depending on the device. Prior to the actual programming operation, the write data must be loaded into the write latches. The basic sequence for RTSP is to set up the Table Pointer, TBLPAG register, and then perform a series of TBLWT instructions to load the write latches. Programming is performed by setting the control bits in the NVMCON register. The number of TBLWTL and TBLWTH instructions needed to load the write latches is equal to the number of program words to be written.

Note: Det anbefales, at TBLPAG-registret gemmes før ændring og gendannes efter brug.

FORSIGTIGHED

På nogle enheder gemmes konfigurationsbittene på den sidste side af programmets Flash-brugerhukommelsesplads i et afsnit kaldet "Flash-konfigurationsbytes". Med disse enheder slettes Flash-konfigurationsbytene, hvis du udfører en sidesletning på den sidste side i programhukommelsen, hvilket muliggør kodebeskyttelse. Derfor bør brugere ikke udføre sidesletningshandlinger på den sidste side i programhukommelsen. Dette er ikke et problem, når konfigurationsbits er gemt i konfigurationshukommelsespladsen i et afsnit kaldet "Enhedskonfigurationsregistre". Se Program Memory Map i kapitlet "Memory Organization" i det specifikke enhedsdatablad for at bestemme, hvor konfigurationsbits er placeret.

Flash-programmeringsoperationer

A program or erase operation is necessary for programming or erasing the internal Flash program memory in RTSP mode. The program or erase operation is automatically timed by the device (refer to the specific device data sheet for timing information). Setting the WR bit (NVMCON[15]) starts the operation. The WR bit is automatically cleared when the operation is finished. The CPU stalls until the programming operation is finished. The CPU will not execute any instructions or respond to interrupts during this time. If any interrupts occur during the programming cycle, they will remain pending until the cycle completes. Some dsPIC33/PIC24 devices may provide auxiliary Flash program memory (refer to the “Memory Organization” chapter of the specific device data sheet for details), which allows instruction execution without CPU Stalls while user Flash program memory is being erased and/ or programmed. Conversely, auxiliary Flash program memory can be programmed without CPU Stalls, as long as code is executed from the user Flash program memory. The NVM interrupt can be used to indicate that the programming operation is complete.

Note

- Hvis en POR- eller BOR-hændelse opstår, mens en RTSP-sletning eller programmeringsoperation er i gang, afbrydes RTSP-handlingen med det samme. Brugeren skal udføre RTSP-handlingen igen, efter at enheden kommer ud af Reset.

- Hvis en EXTR-, SWR-, WDTO-, TRAPR-, CM- eller IOPUWR-nulstillingshændelse opstår, mens en RTSP-sletning eller programmeringshandling er i gang, nulstilles enheden først, efter at RTSP-handlingen er fuldført.

RTSP-PROGRAMMERINGS-ALGORITME

Dette afsnit beskriver RTSP-programmering, som består af tre hovedprocesser.

Oprettelse af et RAM-billede af den dataside, der skal ændres

Udfør disse to trin for at oprette et RAM-billede af den dataside, der skal ændres:

- Læs siden af Flash-programhukommelsen og gem den i data-RAM som et data-"billede". RAM-billedet skal læses fra en sideadressegrænse.

- Rediger RAM-databilledet efter behov.

Erasing Flash Program Memory

Når du har gennemført trin 1 og 2 ovenfor, skal du udføre de følgende fire trin for at slette Flash-programhukommelsessiden:

- Indstil NVMOP[3:0]-bits (NVMCON[3:0]) for at slette siden i Flash-programhukommelsen læst fra trin 1.

- Skriv startadressen på siden, der skal slettes, i NVMADRU- og NMVADR-registrene.

- Med afbrydelser deaktiveret:

- a) Skriv nøglesekvensen til NVMKEY-registret for at aktivere indstilling af WR-bit (NVMCON[15]).

- b) Indstil WR bit; dette vil starte slettecyklussen.

- c) Udfør to NOP-instruktioner.

- WR-bitten ryddes, når slettecyklussen er fuldført.

Programmering af Flash-hukommelsessiden

Den næste del af processen er at programmere Flash-hukommelsessiden. Flash-hukommelsessiden programmeres ved hjælp af dataene fra billedet, der blev oprettet i trin 1. Dataene overføres til skrivelåsene i trin af enten dobbelte instruktionsord eller rækker. Alle enheder har mulighed for dobbelt instruktionsordprogrammering. (Se kapitlet "Flash Program Memory" i det specifikke enhedsdatablad for at bestemme, om og hvilken type rækkeprogrammering der er tilgængelig.) Efter at skrivelåsene er indlæst, påbegyndes programmeringsoperationen, som overfører dataene fra skrivelåse i Flash-hukommelsen. Dette gentages, indtil hele siden er blevet programmeret. Gentag de følgende tre trin, startende ved det første instruktionsord på Flash-siden og trinvis trinvis af enten dobbeltprogramord eller instruktionsrækker, indtil hele siden er blevet programmeret:

- Indlæs skrivelåsene:

- a) Indstil TBLPAG-registret til at pege på placeringen af skrivelåsene.

- b) Indlæs det ønskede antal låse ved hjælp af par af TBLWTL og TBLWTH instruktioner:

- For programmering med dobbeltord kræves to par TBLWTL- og TBLWTH-instruktioner

- Til rækkeprogrammering kræves et par TBLWTL- og TBLWTH-instruktioner for hvert instruktionsordrækkeelement

- Start programmeringsoperationen:

- a) Indstil NVMOP[3:0]-bits (NVMCON[3:0]) til at programmere enten dobbelte instruktionsord eller en instruktionsrække, alt efter hvad der er relevant.

b) Skriv den første adresse på enten det dobbelte instruktionsord eller instruktionsrækken, der skal programmeres i NVMADRU- og NVMADR-registrene.

c) Med afbrydelser deaktiveret:

• Skriv nøglesekvensen til NVMKEY-registret for at aktivere indstilling af WR-bit (NVMCON[15])

• Indstil WR bit; dette vil starte slettecyklussen

• Udfør to NOP-instruktioner

- a) Indstil NVMOP[3:0]-bits (NVMCON[3:0]) til at programmere enten dobbelte instruktionsord eller en instruktionsrække, alt efter hvad der er relevant.

- WR-bitten slettes, når programmeringscyklussen er afsluttet.

Gentag hele processen efter behov for at programmere den ønskede mængde Flash-programhukommelse.

Note

- Brugeren skal huske, at den mindste mængde Flash-programhukommelse, der kan slettes ved hjælp af RTSP, er en enkelt slettet side. Derfor er det vigtigt, at et billede af disse placeringer gemmes i RAM til generelle formål, før en slettecyklus påbegyndes.

- En række eller et ord i Flash-programhukommelsen bør ikke programmeres mere end to gange, før det slettes.

- På enheder med konfigurationsbytes, der er gemt på den sidste side af Flash, rydder udførelse af en sidesletningshandling på den sidste side i programhukommelsen konfigurationsbytes, hvilket muliggør kodebeskyttelse. På disse enheder bør den sidste side i Flash-hukommelsen ikke slettes.

ERASING ONE PAGE OF FLASH

Kodesekvensen vist i Example 4-1 kan bruges til at slette en side i Flash-programhukommelsen. NVMCON-registret er konfigureret til at slette én side programhukommelse. NVMADR- og NMVADRU-registrene indlæses med startadressen på den side, der skal slettes. Programhukommelsen skal slettes ved en "lige" adressegrænse. Se kapitlet "Flash-programhukommelse" i det specifikke enhedsdatablad for at bestemme størrelsen på Flash-siden.

Sletteoperationen påbegyndes ved at skrive en speciel oplåsning eller nøglesekvens til NVMKEY-registret før indstilling af WR-bit (NVMCON[15]). Oplåsningssekvensen skal udføres i den nøjagtige rækkefølge, som vist i eksample 4-1, uden afbrydelse; derfor skal afbrydelser deaktiveres.

To NOP-instruktioner skal indsættes i koden efter slettecyklussen. På visse enheder gemmes konfigurationsbittene på den sidste side af programmet Flash. Med disse enheder sletter udførelse af en sidesletningsoperation på den sidste side i programhukommelsen Flash-konfigurationsbytes, hvilket muliggør kodebeskyttelse som et resultat. Brugere bør ikke udføre sidesletning på den sidste side i programhukommelsen.

LÆSER SKRIVE LÅSE

Skrivelåsene bruges som en lagermekanisme mellem brugerapplikationens tabelskrivninger og den faktiske programmeringssekvens. Under programmeringen overfører enheden data fra skrivelåsene til Flash-hukommelsen. For enheder, der understøtter rækkeprogrammering, f.eksampAfsnit 4-3 viser rækkefølgen af instruktioner, der kan bruges til at indlæse 128 skrivelåse (128 instruktionsord). 128 TBLWTL og 128 TBLWTH instruktioner er nødvendige for at indlæse skrivelåsene til programmering af en række af Flash-programhukommelse. Se kapitlet "Flash Program Memory" i det specifikke enhedsdatablad for at bestemme antallet af programmeringslåse, der er tilgængelige på din enhed. For enheder, der ikke understøtter rækkeprogrammering, f.eksampAfsnit 4-4 viser rækkefølgen af instruktioner, der kan bruges til at indlæse to skrivelåse (to instruktionsord). To TBLWTL- og to TBLWTH-instruktioner er nødvendige for at indlæse skrivelåsene.

Note

- Koden for Load_Write_Latch_Row er vist i Example 4-3 og koden for Load_Write_Latch_Word er vist i Example 4-4. Koden i begge disse examples omtales i efterfølgende examples.

- Se det specifikke enhedsdatablad for antallet af låse.

ENKEL RÆKE PROGRAMMERING EXAMPLE

NVMCON-registret er konfigureret til at programmere én række Flash-programhukommelse. Programoperationen initieres ved at skrive en speciel oplåsning, eller nøglesekvens, til NVMKEY-registret før indstilling af WR-bit (NVMCON[15]). Oplåsningssekvensen skal udføres uden afbrydelse og i den nøjagtige rækkefølge, som vist i eksample 4-5. Derfor skal afbrydelser deaktiveres, før sekvensen skrives.

Note: Ikke alle enheder har mulighed for rækkeprogrammering. Se kapitlet "Flash Program Memory" i det specifikke enhedsdatablad for at afgøre, om denne mulighed er tilgængelig.

To NOP-instruktioner skal indsættes i koden efter programmeringscyklussen.

RÆKKEPROGRAMMERING VED BRUG AF RAM-BUFFEREN

Udvalgte dsPIC33-enheder tillader, at rækkeprogrammering udføres direkte fra et bufferrum i data-RAM i stedet for at gå gennem holdelåsene for at overføre data med TBLWT-instruktioner. Placeringen af RAM-bufferen bestemmes af NVMSRCADR-registrene, som er indlæst med data-RAM-adressen, der indeholder det første ord af programdata, der skal skrives.

Før programoperationen udføres, skal bufferpladsen i RAM indlæses med rækken af data, der skal programmeres. RAM kan indlæses i enten et komprimeret (pakket) eller ukomprimeret format. Komprimeret lagring bruger et dataord til at gemme de mest signifikante bytes (MSB'er) af to tilstødende programdataord. Det ukomprimerede format bruger to dataord for hvert programdataord, hvor den øvre byte af hvert andet ord er 00h. Komprimeret format bruger omkring 3/4 af pladsen i data-RAM sammenlignet med det ukomprimerede format. Ukomprimeret format efterligner på den anden side strukturen af 24-bit programdataordet, komplet med den øverste fantombyte. Dataformatet vælges af RPDF-bit (NVMCON[9]). Disse to formater er vist i figur 4-1.

Når RAM-bufferen er indlæst, indlæses Flash-adressepegerne, NVMADR og NVMADRU, med 24-bit startadressen for den Flash-række, der skal skrives. Som med programmering af skrivelåsene, startes processen ved at skrive NVM-oplåsningssekvensen, efterfulgt af indstilling af WR-bitten. Når den er startet, indlæser enheden automatisk de rigtige låse og inkrementerer NVM-adresseregistrene, indtil alle bytes er blevet programmeret. Eksample 4-7 viser et example af processen. Hvis NVMSRCADR er indstillet til en værdi, således at der opstår en dataunderløbsfejltilstand, vil URERR-bitten (NVMCON[8]) blive indstillet til at angive tilstanden.

Enheder, der implementerer RAM-bufferrækkeprogrammering, implementerer også en eller to skrivelåse. Disse indlæses ved hjælp af TBLWT-instruktionerne og bruges til at udføre ordprogrammeringsoperationer.

ORDPROGRAMMERING

NVMCON-registret er konfigureret til at programmere to instruktionsord i Flash-programhukommelsen. Programoperationen initieres ved at skrive en speciel oplåsning, eller nøglesekvens, til NVMKEY-registret før indstilling af WR-bit (NVMCON[15]). Oplåsningssekvensen skal udføres i den nøjagtige rækkefølge, som vist i eksample 4-8, uden afbrydelse. Derfor bør afbrydelser deaktiveres, før sekvensen skrives.

To NOP-instruktioner skal indsættes i koden efter programmeringscyklussen.

Skrivning til enhedskonfigurationsregistre

På visse enheder gemmes konfigurationsbittene i konfigurationshukommelsespladsen i en sektion kaldet "Device Configuration Registers". På andre enheder gemmes konfigurationsbittene på den sidste side af programmets Flash-brugerhukommelsesplads i et afsnit kaldet "Flash Configuration Bytes". Med disse enheder slettes Flash-konfigurationsbytene, hvis du udfører en sidesletning på den sidste side i programhukommelsen, hvilket muliggør kodebeskyttelse. Derfor bør brugere ikke udføre sidesletningshandlinger på den sidste side i programhukommelsen. Se Program Memory Map i kapitlet "Memory Organization" i det specifikke enhedsdatablad for at bestemme, hvor konfigurationsbits er placeret.

Når konfigurationsbittene er gemt i konfigurationshukommelsespladsen, kan RTSP bruges til at skrive til enhedens konfigurationsregistre, og RTSP tillader, at hvert konfigurationsregister omskrives individuelt uden først at udføre en slettecyklus. Der skal udvises forsigtighed ved skrivning af konfigurationsregistrene, da de styrer kritiske enhedsdriftsparametre, såsom systemurkilden, PLL og WDT-aktivering.

Proceduren for programmering af et enhedskonfigurationsregister ligner proceduren for programmering af Flash-programhukommelse, bortset fra at der kun kræves TBLWTL-instruktioner. Dette skyldes, at de øverste otte bits i hvert enhedskonfigurationsregister er ubrugte. Ydermere skal bit 23 i tabelskriveadressen indstilles for at få adgang til konfigurationsregistrene. Se "Device Configuration" (DS70000618) i "dsPIC33/PIC24 Family Reference Manual" og kapitlet "Special Features" i det specifikke enhedsdatablad for en fuldstændig beskrivelse af enhedskonfigurationsregistrene.

Note

- Skrivning til enhedskonfigurationsregistre er ikke tilgængelig på alle enheder. Se kapitlet "Special Features" i det specifikke enhedsdatablad for at bestemme de tilstande, der er tilgængelige i henhold til de enhedsspecifikke NVMOP[3:0]-bits definition.

- Mens der udføres RTSP på enhedskonfigurationsregistre, skal enheden fungere ved hjælp af den interne FRC Oscillator (uden PLL). Hvis enheden opererer fra en anden klokkilde, skal der udføres en klokomskifter til den interne FRC-oscillator (NOSC[2:0] = 000), før RTSP-operation udføres i enhedens konfigurationsregistre.

- Hvis Primary Oscillator Mode Select bits (POSCMD[1:0]) i Oscillator Configuration register (FOSC) omprogrammeres til en ny værdi, skal brugeren sikre, at Clock Switching Mode bits (FCKSM[1:0]) i FOSC-registret har en indledende programmeret værdi på '0', før denne RTSP-operation udføres.

KONFIGURATION REGISTRER SKRIVE ALGORITIME

Den generelle procedure er som følger:

- Skriv den nye konfigurationsværdi til Table Write-låsen ved hjælp af en TBLWTL-instruktion.

- Konfigurer NVMCON til en konfigurationsregisterskrivning (NVMCON = 0x4000).

- Skriv adressen på det konfigurationsregister, der skal programmeres i NVMADRU- og NVMADR-registrene.

- Deaktiver interrupts, hvis aktiveret.

- Skriv nøglesekvensen til NVMKEY-registret.

- Start skrivesekvensen ved at indstille WR bit (NVMCON[15]).

- Genaktiver afbrydelser, hvis det er nødvendigt.

Exampside 4-10 viser den kodesekvens, der kan bruges til at ændre et enhedskonfigurationsregister.

REGISTRER KORT

En oversigt over de registre, der er forbundet med Flash-programmering, findes i Tabel 5-1.

Dette afsnit viser applikationsnoter, der er relateret til dette afsnit af manualen. Disse applikationsnoter er muligvis ikke skrevet specifikt til dsPIC33/PIC24 produktfamilierne, men koncepterne er relevante og kan bruges med modifikationer og mulige begrænsninger. De aktuelle applikationsbemærkninger relateret til Flash-programmering er:

Note: Besøg venligst mikrochippen webwebsted (www.microchip.com) for yderligere applikationsbemærkninger og kode examples til dsPIC33/PIC24-familierne af enheder.

REVISIONSHISTORIE

Revision A (august 2009)

Dette er den første udgivne version af dette dokument.

Revision B (februar 2011)

Denne revision indeholder følgende opdateringer:

- Examples:

- Fjernet eksample 5-3 og Example 5-4

- Opdateret eksample 4-1, Example 4-5 og Example 4-10

- Eventuelle referencer til #WR blev opdateret til #15 i Example 4-1, Example 4-5 og Example 4-8

- Opdateret følgende i Exampaf 4-3:

- Opdaterede titlen "Word Programming" til "Loading Write Latches for Row Programming"

- Enhver henvisning til #ram_image blev opdateret til #0xFA

- Tilføjet eksample 4-4

- Opdaterede titlen i Example 4-8

- Bemærkninger:

- Tilføjet to bemærkninger i afsnit 4.2 "Flash-programmeringsoperationer"

- Opdaterede noten i afsnit 4.5.2 "Indlæser skrivelåse"

- Tilføjet tre bemærkninger i afsnit 4.6 "Skrivning til enhedskonfigurationsregistre"

- Tilføjet note 1 i tabel 5-1

- registre:

- Opdaterede bitværdierne for NVMOP[3:0]: NVM Operation Vælg bits i Flash Memory Control (NVMCON) registeret (se register 3-1)

- Sektioner:

- Fjernede afsnit 5.2.1.4 "Skrive Word Mode" og 5.2.1.5 "Skrive Byte Mode"

- Opdateret afsnit 3.0 "Kontrolregistre"

- Opdateret følgende i afsnit 4.5.5 "Word Programmering":

- Ændrede afsnitstitlen "Programmering af ét ord i Flash-hukommelse" til "Word Programmering"

- Opdateret første afsnit

- Ændrede udtrykkene "et ord" til "et par ord" i andet afsnit

- Tilføjet et nyt trin 1 til afsnit 4.6.1 "Konfigurationsregisterskrivealgoritme"

- Tabeller:

- Opdateret tabel 5-1

- Nogle få referencer til programhukommelse blev opdateret til Flash-programhukommelse

- Andre mindre opdateringer såsom sprog- og formateringsopdateringer blev indarbejdet i hele dokumentet

Revision C (juni 2011)

Denne revision indeholder følgende opdateringer:

- Examples:

- Opdateret eksample 4-1

- Opdateret eksample 4-8

- Bemærkninger:

- Tilføjet en note i afsnit 4.1 "RTSP Operation"

- Tilføjet note 3 i afsnit 4.2 "Flash-programmeringsoperationer"

- Tilføjet note 3 i afsnit 4.2.1 "RTSP-programmeringsalgoritme"

- Added a note in Section 4.5.1 “Erasing One Page of Flash”

- Tilføjet note 2 i afsnit 4.5.2 "Indlæser skrivelåse"

- registre:

- Opdaterede bitbeskrivelsen for bit 15-0 i det ikke-flygtige hukommelsesadresseregister (se register 3-3)

- Sektioner:

- Opdateret afsnit 4.1 "RTSP-drift"

- Opdateret afsnit 4.5.5 "Word Programmering"

- Andre mindre opdateringer såsom sprog- og formateringsopdateringer blev indarbejdet i hele dokumentet

Revision D (december 2011)

Denne revision indeholder følgende opdateringer:

- Opdateret afsnit 2.1.3 "Tabel skrivelåse"

- Opdateret afsnit 3.2 "NVMKEY Register"

- Opdaterede noterne i NVMCON: Flash Memory Control Register (se Register 3-1)

- Der blev foretaget omfattende opdateringer i hele afsnit 4.0 "Run-Time Self-Programming (RTSP)"

- Andre mindre opdateringer såsom sprog- og formateringsopdateringer blev indarbejdet i hele dokumentet

Revision E (oktober 2018)

Denne revision indeholder følgende opdateringer:

- Tilføjet eksample 2-2, Example 4-2, Example 4-6 og Example 4-9

- Tilføjet afsnit 4.5.4 "Rækkeprogrammering ved hjælp af RAM-bufferen"

- Opdateret sektion 1.0 "Introduktion", sektion 3.3 "NVM-adresseregistre", sektion 4.0 "Run-Time Self-Programming (RTSP)" og sektion 4.5.3 "Single Row Programmering Ex.ampdet"

- Opdateret register 3-1

- Opdateret eksample 4-7

- Opdateret tabel 5-1

Revision F (november 2021)

Tilføjet afsnit 3.2.1 "Deaktivering af afbrydelser".

Opdateret eksample 3-1, Example 4-1, Example 4-2, Example 4-5, Example 4-6, Example 4-7, Example 4-8, Example 4-9 og Example 4-10.

Updated Section 3.2 “NVMKEY Register”, Section 4.5.1 “Erasing One Page of Flash”, Section 4.5.3 “Single Row Programming Example” og afsnit 4.6.1 “Konfigurationsregisterskrivealgoritme”.

Bemærk følgende detaljer om kodebeskyttelsesfunktionen på Microchip-produkter:

- Microchip-produkter opfylder specifikationerne i deres særlige Microchip-datablad.

- Microchip mener, at dens familie af produkter er sikre, når de bruges på den tilsigtede måde, inden for driftsspecifikationerne og under normale forhold.

- Microchip værdsætter og beskytter aggressivt sine intellektuelle ejendomsrettigheder. Forsøg på at bryde kodebeskyttelsesfunktionerne i Microchip-produktet er strengt forbudt og kan være i strid med Digital Millennium Copyright Act.

- Hverken Microchip eller nogen anden halvlederproducent kan garantere sikkerheden af deres kode. Kodebeskyttelse betyder ikke, at vi garanterer, at produktet er "ubrydeligt". Kodebeskyttelse er i konstant udvikling. Microchip er forpligtet til løbende at forbedre kodebeskyttelsesfunktionerne i vores produkter

Denne publikation og oplysningerne heri må kun bruges med Microchip-produkter, herunder til at designe, teste og integrere Microchip-produkter med din applikation. Brug af disse oplysninger på anden måde overtræder disse vilkår. Oplysninger om enhedsapplikationer gives kun for din bekvemmelighed og kan blive afløst af opdateringer. Det er dit ansvar at sikre, at din ansøgning lever op til dine specifikationer. Kontakt dit lokale Microchip salgskontor for yderligere support, eller få yderligere support på https://www.microchip.com/en-us/support/design-help/client-supportservices.

DISSE OPLYSNINGER LEVERES AF MICROCHIP "SOM DE ER". MICROCHIP GIVER INGEN REPRÆSENTATIONER ELLER GARANTIER AF NOGEN ART, HVERKEN UDTRYKKELIGE ELLER UNDERFORSTÅEDE, SKRIFTLIGE ELLER mundtlige, LOVBESTEMMET ELLER PÅ ANDEN MÅDE, RELATET TIL OPLYSNINGERNE, HERUNDER MEN IKKE BEGRÆNSET TIL NOGEN UNDERFORSTÅEDE GARANTIER OG ANSVARLIGHEDER ULAR FORMÅL ELLER GARANTIER RELATET TIL DETS TILSTAND, KVALITET ELLER YDELSE. MICROCHIP VIL UNDER INGEN OMSTÆNDIGHEDER VÆRE ANSVARLIG FOR NOGEN INDIREKTE, SÆRLIGE, STRAFFENDE, TILFÆLDELIGE ELLER FØLGETAB, SKADER, OMKOSTNINGER ELLER UDGIFTER AF NOGEN ART, SOM ER RELATET TIL OPLYSNINGERNE ELLER DERES ANVENDELSE, UNDER ANDET ELLER ARGANG. MULIGHEDEN ELLER SKADERNE ER FORUDSUELIGE. I DET FULDSTÆNDE OMFANG, DET ER TILLADT AF LOVEN, VIL MICROCHIPS SAMLEDE ANSVAR PÅ ALLE KRAV PÅ NOGEN MÅDE RELATET TIL INFORMATIONEN ELLER DERES ANVENDELSE IKKE OVERstige BELØBET, HVIS NOGET, SOM DU HAR BETALT DIREKTE TIL MICRATIONOCHIP.

Brug af Microchip-enheder i livsstøtte- og/eller sikkerhedsapplikationer er helt på købers risiko, og køberen indvilliger i at forsvare, skadesløsholde og holde Microchip skadesløs fra enhver skade, krav, sager eller udgifter som følge af sådan brug. Ingen licenser videregives, implicit eller på anden måde, under nogen af Microchips intellektuelle ejendomsrettigheder, medmindre andet er angivet.

For information om Microchips kvalitetsstyringssystemer, besøg venligst www.microchip.com/quality.

Varemærker

Mikrochipnavnet og logoet, Microchip-logoet, Adaptec, AnyRate, AVR, AVR-logoet, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi-logo, MOST, MOST-logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32-logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST-logo, SuperFlash , Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron og XMEGA er registrerede varemærker tilhørende Microchip Technology Incorporated i USA og andre lande. AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, WinPath og ZL er registrerede varemærker tilhørende Microchip Technology Incorporated i USA

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic DAMage Matching , ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, NVM Express, NVMe, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL . , Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-IS, storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect og ZENA er varemærker tilhørende Microchip Technology Incorporated i USA og andre lande.

SQTP er et servicemærke tilhørende Microchip Technology Incorporated i USA

Adaptec-logoet, Frequency on Demand, Silicon Storage Technology, Symmcom og Trusted Time er registrerede varemærker tilhørende Microchip Technology Inc. i andre lande.

GestIC er et registreret varemærke tilhørende Microchip Technology Germany II GmbH & Co. KG, et datterselskab af Microchip Technology Inc., i andre lande.

Alle andre varemærker nævnt heri tilhører deres respektive virksomheder.

© 2009-2021, Microchip Technology Incorporated og dets datterselskaber.

Alle rettigheder forbeholdes.

ISBN: 978-1-5224-9314-3

Verdensomspændende salg og service

AMERIKA

- Virksomhedskontor

2355 West Chandler Blvd.

Chandler, AZ 85224-6199

Tlf.: 480-792-7200

Fax: 480-792-7277

Teknisk support: http://www.microchip.com/

støtte Web Adresse: www.microchip.com - Atlanta

Duluth, GA

Tlf.: 678-957-9614

Fax: 678-957-1455 - Austin, TX

Tlf.: 512-257-3370 - Boston

Westborough, MA

Tlf.: 774-760-0087

Fax: 774-760-0088 - Chicago

Itasca, IL

Tlf.: 630-285-0071

Fax: 630-285-0075 - Dallas

Addison, TX

Tlf.: 972-818-7423

Fax: 972-818-2924 - Detroit

Novi, MI

Tlf.: 248-848-4000 - Houston, TX

Tlf.: 281-894-5983 - Indianapolis

Noblesville, IN

Tlf.: 317-773-8323

Fax: 317-773-5453

Tlf.: 317-536-2380 - Los Angeles

Mission Viejo, CA

Tlf.: 949-462-9523

Fax: 949-462-9608

Tlf.: 951-273-7800 - Raleigh, NC

Tlf.: 919-844-7510 - New York, NY

Tlf.: 631-435-6000 - San Jose, CA

Tlf.: 408-735-9110

Tlf.: 408-436-4270 - Canada – Toronto

Tlf.: 905-695-1980

Fax: 905-695-2078

ASIEN/PACIFIK

- Australien – Sydney

Tlf.: 61-2-9868-6733 - Kina – Beijing

Tlf.: 86-10-8569-7000 - Kina – Chengdu

Tlf.: 86-28-8665-5511 - Kina – Chongqing

Tlf.: 86-23-8980-9588 - Kina – Dongguan

Tlf.: 86-769-8702-9880 - Kina – Guangzhou

Tlf.: 86-20-8755-8029 - Kina – Hangzhou

Tlf.: 86-571-8792-8115 - Kina – Hong Kong SAR

Tlf.: 852-2943-5100 - Kina – Nanjing

Tlf.: 86-25-8473-2460 - Kina – Qingdao

Tlf.: 86-532-8502-7355 - Kina – Shanghai

Tlf.: 86-21-3326-8000 - Kina – Shenyang

Tlf.: 86-24-2334-2829 - Kina – Shenzhen

Tlf.: 86-755-8864-2200 - Kina – Suzhou

Tlf.: 86-186-6233-1526 - Kina – Wuhan

Tlf.: 86-27-5980-5300 - Kina – Xian

Tlf.: 86-29-8833-7252 - Kina – Xiamen

Tlf.: 86-592-2388138 - Kina – Zhuhai

Tlf.: 86-756-3210040 - Indien – Bangalore

Tlf.: 91-80-3090-4444 - Indien – New Delhi

Tlf.: 91-11-4160-8631 - Indien - Pune

Tlf.: 91-20-4121-0141 - Japan – Osaka

Tlf.: 81-6-6152-7160 - Japan – Tokyo

Tlf.: 81-3-6880-3770 - Korea – Daegu

Tlf.: 82-53-744-4301 - Korea – Seoul

Tlf.: 82-2-554-7200 - Malaysia - Kuala Lumpur

Tlf.: 60-3-7651-7906 - Malaysia – Penang

Tlf.: 60-4-227-8870 - Filippinerne – Manila

Tlf.: 63-2-634-9065 - Singapore

Tlf.: 65-6334-8870 - Taiwan – Hsin Chu

Tlf.: 886-3-577-8366 - Taiwan – Kaohsiung

Tlf.: 886-7-213-7830 - Taiwan - Taipei

Tlf.: 886-2-2508-8600 - Thailand – Bangkok

Tlf.: 66-2-694-1351 - Vietnam – Ho Chi Minh

Tlf.: 84-28-5448-2100

EUROPA

- Østrig – Wels

Tlf.: 43-7242-2244-39

Fax: 43-7242-2244-393 - Danmark – København

Tlf.: 45-4485-5910

Fax: 45-4485-2829 - Finland – Espoo

Tlf.: 358-9-4520-820 - Frankrig – Paris

Tlf.: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79 - Tyskland – Garching

Tlf.: 49-8931-9700 - Tyskland – Haan

Tlf.: 49-2129-3766400 - Tyskland – Heilbronn

Tlf.: 49-7131-72400 - Tyskland – Karlsruhe

Tlf.: 49-721-625370 - Tyskland – München

Tlf.: 49-89-627-144-0

Fax: 49-89-627-144-44 - Tyskland – Rosenheim

Tlf.: 49-8031-354-560 - Italien – Milano

Tlf.: 39-0331-742611

Fax: 39-0331-466781 - Italien – Padova

Tlf.: 39-049-7625286 - Holland – Drunen

Tlf.: 31-416-690399

Fax: 31-416-690340 - Norge – Trondheim

Tlf.: 47-7288-4388 - Polen – Warszawa

Tlf.: 48-22-3325737 - Rumænien – Bukarest

Tlf.: 40-21-407-87-50 - Spanien - Madrid

Tlf.: 34-91-708-08-90

Fax: 34-91-708-08-91 - Sverige – Göteborg

Tlf.: 46-31-704-60-40 - Sverige – Stockholm

Tlf.: 46-8-5090-4654 - Storbritannien – Wokingham

Tlf.: 44-118-921-5800

Fax: 44-118-921-5820

Note:

Dette afsnit i familiereferencemanualen er beregnet til at tjene som et supplement til enhedens datablade. Afhængigt af enhedsvarianten gælder dette manualsektion muligvis ikke for alle dsPIC33/PIC24-enheder. Se venligst bemærkningen i begyndelsen af kapitlet "Flash Program Memory" i det aktuelle enhedsdatablad for at kontrollere, om dette dokument understøtter den enhed, du bruger.

Enhedsdatablade og familiereferencemanualsektioner er tilgængelige for download fra Microchip Worldwide Webwebsted på: http://www.microchip.com.

Dokumenter/ressourcer

|

MICROCHIP PIC24 Flash-programmering [pdfBrugervejledning PIC24 Flash-programmering, PIC24, Flash-programmering, programmering |

|

MICROCHIP PIC24 Flash-programmering [pdfBrugervejledning PIC24 Flash-programmering, PIC24, Flash-programmering |