intel High-Level Synthesis Compiler Pro Edition

Produktinformation

| Produktnavn | Intel High-Level Synthesis Compiler Pro Edition |

|---|---|

| Version | 22.4 |

| Udgivelsesdato | 19. december 2022 |

| Meddelelse om afskrivning | Intel High-Level Synthesis Compiler er planlagt til at være forældet efter version 23.4. |

Produktbrugsvejledning

Kom godt i gang Guide

- Initialiser dit compilermiljø.

- Review de forskellige design exampfiler og selvstudier, der følger med Intel HLS-kompileren.

Brugervejledning

- Brugervejledningen giver instruktioner om

- Syntetisering, verifikation og simulering af intellektuel ejendom (IP) designet til Intel FPGA-produkter.

- Gennemgå hele udviklingsforløbet af din komponent fra oprettelse af din komponent og testbench til integration af din komponent-IP i et større system med Intel Quartus Prime-softwaren.

Vejledning til bedste praksis

Vejledningen til bedste praksis indeholder teknikker og praksis, som du kan anvende til at forbedre FPGA-arealudnyttelsen og ydeevnen af din HLS-komponent. Anvend disse bedste fremgangsmåder efter at have verificeret din komponents funktionelle rigtighed.

Referencemanual

Referencemanualen giver referenceoplysninger om de funktioner, der understøttes af Intel HLS Compiler. Find detaljer om Intel HLS Compiler-kommandoindstillinger, overskrift files, pragmaer, attributter, makroer, erklæringer, argumenter og skabelonbiblioteker.

Intel® High Level Synthesis Compiler Pro Edition Version 22.4 Release Notes

- Intel® High Level Synthesis Compiler Pro Edition-udgivelsesbemærkningerne giver de seneste oplysninger om Intel High Level Synthesis Compiler Pro Edition version 22.4.

Afventer udfasning af Intel HLS-kompileren

- For at bevare adgangen til de nyeste FPGA-designfunktioner på højt niveau, optimeringer og udviklingsværktøjer, skal du migrere dine eksisterende designs for at bruge Intel oneAPI Base Toolkit.

- Intel High Level Synthesis (HLS) Compiler er planlagt til at blive udfaset efter version 23.4.

- Besøg Intel oneAPI-produktsiden for migreringsråd, eller gå til Intel High Level Design-fællesskabsforum for spørgsmål eller anmodninger.

Om Intel HLS Compiler Pro Edition dokumentationsbibliotek

- Dokumentationen til Intel HLS Compiler Pro Edition er opdelt på nogle få publikationer. Brug følgende tabel til at finde den publikation, der indeholder oplysninger om Intel HLS Compiler Pro Edition, som du leder efter:

Tabel 1. Intel High-Level Synthesis Compiler Pro Edition dokumentationsbibliotek

| Titel og beskrivelse | |

| Release Notes

Giver seneste oplysninger om Intel HLS Compiler. |

Forbindelse |

| Kom godt i gang Guide

Kom i gang med Intel HLS Compiler ved at lære, hvordan du initialiserer dit compilermiljø og reviewing de forskellige design exampfiler og selvstudier, der følger med Intel HLS-kompileren. |

Forbindelse |

| Brugervejledning

Indeholder instruktioner om at syntetisere, verificere og simulere intellektuel ejendom (IP), som du designer til Intel FPGA-produkter. Gå gennem hele udviklingsforløbet af din komponent fra oprettelse af din komponent og testbench til integration af din komponent-IP i et større system med Intel Quartus Prime-softwaren. |

Forbindelse |

| Vejledning til bedste praksis

Giver teknikker og praksis, som du kan anvende til at forbedre FPGA-arealudnyttelsen og ydeevnen af din HLS-komponent. Typisk anvender du disse bedste fremgangsmåder, efter du har bekræftet din komponents funktionelle rigtighed. |

Forbindelse |

| Referencemanual

Giver referenceoplysninger om de funktioner, der understøttes af Intel HLS Compiler. Find detaljer om Intel HLS Compiler-kommandoindstillinger, overskrift files, pragmaer, attributter, makroer, erklæringer, argumenter og skabelonbiblioteker. |

Forbindelse |

Intel Corporation. Alle rettigheder forbeholdes. Intel, Intel-logoet og andre Intel-mærker er varemærker tilhørende Intel Corporation eller dets datterselskaber. Intel garanterer ydeevnen af sine FPGA- og halvlederprodukter i henhold til de aktuelle specifikationer i overensstemmelse med Intels standardgaranti, men forbeholder sig retten til at foretage ændringer af produkter og tjenester til enhver tid uden varsel. Intel påtager sig intet ansvar eller erstatningsansvar som følge af applikationen eller brugen af oplysninger, produkter eller tjenester beskrevet heri, undtagen som udtrykkeligt skriftligt aftalt af Intel. Intel-kunder rådes til at indhente den seneste version af enhedsspecifikationerne, før de stoler på nogen offentliggjort information, og før de afgiver ordrer på produkter eller tjenester.

*Andre navne og mærker kan hævdes at være andres ejendom.

Afventer udfasning af Intel HLS-kompileren

- For at bevare adgangen til de nyeste FPGA-designfunktioner på højt niveau, optimeringer og udviklingsværktøjer, skal du migrere dine eksisterende designs for at bruge Intel oneAPI Base Toolkit.

- Intel High Level Synthesis (HLS) Compiler er planlagt til at blive udfaset efter version 23.4.

- Besøg Intel oneAPI-produktsiden for migreringsråd, eller gå til Intel High Level Design-fællesskabsforum for spørgsmål eller anmodninger.

Nye funktioner og forbedringer

- Intel High Level Synthesis Compiler Pro Edition version 22.4 indeholder følgende nye funktioner:

- Vedligeholdelsesfrigivelse.

- Ingen nye funktioner eller forbedringer til Intel HLS Compiler Pro Edition Version 22.4.

Ændringer i softwareadfærd

- Dette afsnit dokumenterer tilfælde, hvor funktionerne i Intel HLS Compiler Pro Edition version 22.4 er ændret i forhold til tidligere udgivelser af compileren.

Vedligeholdelsesfrigivelse.

- Ingen ændringer i softwareadfærd for Intel HLS Compiler Pro Edition Version 22.4.

Intel High-Level Synthesis Compiler Pro Edition Forudsætninger

- Intel HLS Compiler Pro Edition er en del af Intel Quartus® Prime Pro Edition Design Suite. Du kan installere Intel HLS Compiler som en del af din Intel Quartus Prime-softwareinstallation eller installere den separat. Det kræver Intel Quartus Prime og yderligere software at bruge.

- For detaljerede instruktioner om installation af Intel Quartus Prime Pro Edition-software, inklusive systemkrav, forudsætninger og licenskrav, se Intel FPGA-softwareinstallation og -licens.

- Intel HLS Compiler kræver følgende software ud over Intel Quartus Prime:

C++ compiler

- På Linux kræver Intel HLS Compiler GCC 9.3.0 inklusive GNU C++-biblioteket og binære hjælpeprogrammer (binutils).

- Denne version af GCC leveres som en del af din Intel HLS Compiler-installation. Efter installation af Intel HLS Compiler, er GCC 9.3.0 tilgængelig i /gcc.

- Vigtig: Intel HLS-kompileren bruger /gcc bibliotek som dets værktøjskædemappe. Brug denne installation af GCC til alt dit HLS-relaterede designarbejde.

- For Windows skal du installere en af følgende versioner af Microsoft* Visual Studio* Professional:

- Microsoft Visual Studio 2017 Professional

- Microsoft Visual Studio 2017-fællesskab

- For at få den mest opdaterede C++17-support skal du sikre dig, at du bruger den seneste version af Visual Studio 2017.

- Vigtig: Intel HLS Compiler-softwaren understøtter ikke andre versioner af Microsoft Visual Studio end dem, der er specificeret for udgaven af softwaren.

Siemens* EDA Questa®-simuleringssoftware

- På Windows- og RedHat Linux-systemer kan du installere Questa®-simuleringssoftwaren fra Intel Quartus Prime-softwareinstallationsprogrammet. De tilgængelige muligheder er som følger:

- Questa Intel FPGA Edition

- Questa Intel FPGA Starter Edition

- Både Questa Intel FPGA Edition og Questa Intel FPGA Starter Edition kræver licenser. Licensen til Questa Intel FPGA Starter Edition er gratis. For detaljer henvises til Intel FPGA-softwareinstallation og -licens.

- Alternativt kan du bruge din egen licenserede version af Siemens* EDA ModelSim* SE eller Siemens EDA Questa Advanced Simulator-software.

- På Linux-systemer kræver Questa – Intel FPGA Edition og Questa – Intel FPGA Starter Edition Red Hat*-udviklingsværktøjspakkerne.

- For information om alle ModelSim- og Questa-softwareversioner, som Intel-softwaren understøtter, henvises til afsnittet EDA Interface Information i Software and Device Support Release Notes for din udgave af Intel Quartus Prime Pro Edition.

Relateret information

- Intel High Level Synthesis Compiler Kom godt i gang Guide

- Understøttede operativsystemer

- Softwarekrav i Intel FPGA-softwareinstallation og -licens

- EDA Interface Information (Intel Quartus Prime Pro Edition)

Kendte problemer og løsninger

- Dette afsnit indeholder oplysninger om kendte problemer, der påvirker Intel HLS Compiler Pro Edition version 22.4.

| Beskrivelse | Løsning |

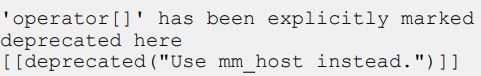

| Når du bruger den forældede klasse mm_master, udsender compileren en advarselsmeddelelse som følgende:

Denne meddelelse angiver ikke, hvilken del af din kode der skal ændres. |

Undgå denne advarselsmeddelelse ved at bruge klassen mm_host, som erstatter den forældede klasse mm_master. |

| (Kun Windows) Kompilering af et design i en mappe med et langt stinavn kan resultere i kompileringsfejl.

Tjek debug.log file for "ikke kunne finde file" fejl. Disse fejl kan indikere, at din sti er for lang. |

Kompiler designet i en mappe med et kort stinavn. |

| (Kun Windows) En lang sti til din Intel Quartus Prime installationsmappe kan forhindre dig i at kompilere og køre Intel HLS Compiler tutorials og ex.ample designs.

Tjek debug.log file for "ikke kunne finde file" fejl. Disse fejl kan indikere, at din sti er for lang. |

Flyt tutorials og examples til et kort stinavn, før du prøver at køre dem. |

| Beskrivelse | Løsning |

| Biblioteker, der er målrettet mod OpenCL* og er skrevet i HLS, kan ikke bruge streams eller pipes som en grænseflade mellem OpenCL-kode og biblioteket skrevet i HLS.

Biblioteket i HLS kan dog bruge streams eller rør, hvis begge endepunkter er inden for biblioteket (f.eks.ample, en strøm, der forbinder to opgavefunktioner). |

N/A |

| Anvendelse af parameteren ihc::maxburst på Avalon® Memory-Mapped værtsgrænseflader kan få dit design til at hænge i simulering. | N/A |

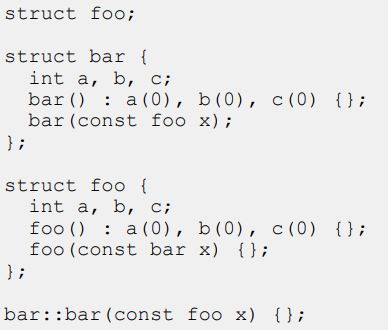

| I nogle usædvanlige tilfælde, hvis du har to klasser, hvis konstruktører hver kræver forekomster af den anden klasse som input, kan compileren gå ned.

F.eksample, kompilering af følgende kodestykke får compileren til at gå ned:

|

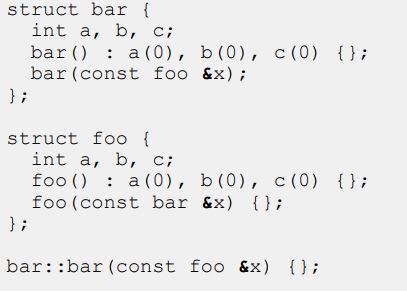

Undgå at skabe en cirkulær definition. Brug i stedet en pointer eller reference i din kopikonstruktør.

F.eksample, transformer det tidligere kodestykke til følgende kode og indsend strukturen som en reference til konstruktøren:

|

| Biblioteker, der målretter mod OpenCL og er skrevet i HLS, kan forårsage, at OpenCL-kerner, der inkluderer biblioteket, har en mere konservativ inkrementel kompilering. | N/A |

| Når du udvikler et bibliotek, hvis du har en #define, der definerer en værdi, som du bruger senere i en #pragma, fejler kommandoen fpga_crossgen.

F.eksample, kan følgende kode ikke kompileres af

|

Brug pragma i stedet for #pragma.

F.eksample, følgende kompileres med succes med

|

| Når du bruger kommandoen -c til at have separate kompilerings- og sammenkædnings-stages i din arbejdsgang, og hvis du ikke angiver -march-indstillingen i link-stage (eller angiv en anden værdi for -march-option), din kobling stage kan mislykkes med eller uden fejlmeddelelser. | Sørg for, at du bruger den samme -march-indstillingsværdi til både kompileringen med -c-kommandoindstillingen stage og de forbindende stage. |

| Beskrivelse | Løsning |

| Anvendelse af hukommelsesattributten hls_merge på et array, der er erklæret i en udrullet eller delvist udrullet sløjfe, får kopier af arrayet til at blive flettet på tværs af de udrullede sløjfe-iterationer.

|

Undgå at bruge hukommelsesattributten hls_merge i udrullede sløjfer.

Hvis du har brug for at flette hukommelser i en udrullet sløjfe, skal du udtrykkeligt erklære et array af struct-type til breddesammenfletning eller erklære et dybere array til dybdesammenfletning.

|

| I funktionshukommelsen ViewI en designrapport på højt niveau kan nogle funktionsbestemte hukommelser se ud som "optimeret væk". | Ingen.

Når en file indeholder funktioner, der er komponenter og funktioner, der ikke er komponenter, alle funktionsomfangsvariable er opført i ruden Funktionshukommelsesliste, men kun variabler fra komponenter har information om dem at vise i funktionshukommelsen View rude. |

| Nogle designrapporter på højt niveau mislykkes i Microsoft Internet Explorer*. | Brug en af følgende browsere til at view rapporterne:

• Google Chrome* • Microsoft Edge* • Mozilla* Firefox* |

| Løkken Viewer i High-Level Design Reports har følgende begrænsninger:

• Opførselen af båsfrie klynger er ikke modelleret i løkken Vieweh. Den endelige latenstid vist i løkken Viewer for en stall-fri klynge er typisk mere pessimistisk (det vil sige højere) end den faktiske latency af dit design. For beskrivelse af klyngedannelse og båsfrie klynger henvises til Klynger af datastien i Intel på højt niveau Synthesis Compiler Pro Edition Vejledning til bedste praksis. • Båse fra læsninger og skrivninger fra hukommelsen eller udskriftsudsagn modelleres ikke. • Høje iterationstal (>1000) forårsager langsom ydeevne af løkken Vieweh. • Du kan ikke angive en iterationstælling på nul (0) i løkken Vieweh. |

Ingen. |

| Links i nogle rapporter i High-Level Design Reports genereret på Windows-systemer virker ikke. | Generer designrapporterne på højt niveau (det vil sige kompilér din kode) på et Linux-system. |

| Brug af en struktur af en enkelt ac_int-datatype i en dampende grænseflade, der bruger pakker (ihc::usesPackets ) virker ikke.

F.eksample, følgende kodestykke virker ikke:

|

For at bruge denne kombination i dit design skal du overholde følgende begrænsninger:

• Den interne ac_int-datastørrelse skal være multiplum af 8 • Strømgrænsefladetypeerklæringen skal angive ihc::bitsPerSymbol<8> F.eksample, følgende kodestykke virker:

|

| Beskrivelse | Løsning | |

| Når du kører en high-throughput-simulering af din komponent ved hjælp af enqueue-funktionskald, hvis du ikke bruger funktionen ihc_hls_component_run_all til at køre de ikøede komponentkald efter alle ihc_hls_enqueue-kaldene for den komponent, opstår følgende adfærd:

• I emulering køres de i kø stillede komponentfunktioner. • I simulering køres de stillede komponentfunktioner ikke, uden fejl- eller advarselsmeddelelser. |

Sørg for, at du bruger funktionen ihc_hls_component_run_all, efter at alle ihc_hls_enqueue kalder den komponent til at køre komponentfunktionskald i kø. | |

| Start af en opgavefunktion med ihc::launch_always_run | For at undgå at fjerne optimeringen skal du tilføje et stykke tid(1) | |

| fjerner optimeringsattributter, der er anvendt på opgaven | sløjfe til den berørte funktion anvende den tilsvarende kontrol | |

| fungere. | pragma til while(1)-løkken i stedet for funktionen. | |

| I den følgende kode example, attributten anvendt på funktionen ignoreres. Designrapporterne på højt niveau viser en II på 1 for denne opgave i stedet for den anmodede II på 4. | Følgende kode exampvi viser, hvordan du kan implementere denne ændring for den tidligere kode, f.eksampdet: | |

|

|

|

| For Cyclone® V-projekter, der indeholder flere HLS-komponenter, kan du modtage en fejl, når du bruger kommandoen i++ til at kompilere dit projekt til hardware (i++ -march=CycloneV).

Selvom fejlteksten varierer afhængigt af dit projekt, er fejlsignaturen en Intel Quartus Prime-kompileringsfejl på grund af dårlig Verilog-syntaks. Et modul forsøger at bruge en funktion, som Intel Quartus Prime-kompileren ikke kan finde. |

Hvis du støder på dette problem, skal du placere hver HLS-komponent i et separat projekt. | |

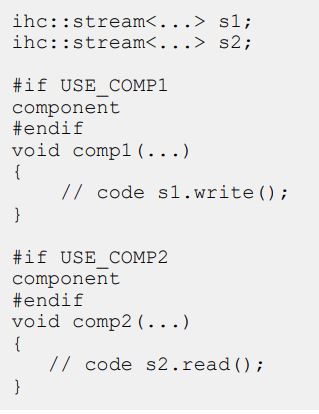

| Kompilering af nogle designs, der indeholder flere komponenter, genererer en fejl om genbrug af stream. | Hvis du støder på dette problem, skal du kompilere hver komponent i designet separat. Du skal muligvis tilføje makroer til din kode for at gøre det muligt for hver komponent at kompilere separat. | |

| Overvej følgende exampdet: | ||

|

||

Intel High-Level Synthesis Compiler Pro Edition Release Notes Arkiver

For de seneste og tidligere versioner af denne brugervejledning henvises til Intel HLS Compiler Pro Edition Release Notes. Hvis en softwareversion ikke er angivet, gælder udgivelsesbemærkningerne for den tidligere softwareversion.

Dokumentrevisionshistorik for Intel HLS Compiler Pro Edition version 22.4 Release Notes

| Dokumentversion | Intel Quartus Prime-version | Ændringer |

| 2022.12.19 | 22.4 | • Første udgivelse. |

Dokumenter/ressourcer

|

intel High Level Synthesis Compiler Pro Edition [pdf] Instruktioner Version 22.4, Version 23.4, High Level Synthesis Compiler Pro Edition, High Level Synthesis Compiler, Pro Edition |